IBM PPC750FX User Manual - page 81

Evaluation Board Manual

Preliminary

PPC750FX Evaluation Board

750FXebm_ch11.fm

June 10, 2003

CPLD Programming

Page 81 of 115

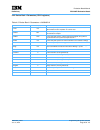

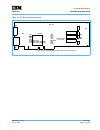

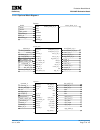

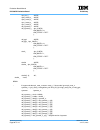

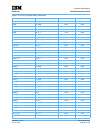

FLASH/SRAM/BIG : NODE; -- boot from SRAM

BIG/SRAM/FLASH : NODE; -- boot BIG, then SRAM, flash on CS0

BIG/FLASH/SRAM : NODE; -- boot BIG, then flash, SRAM on CS0

halfclk

: NODE;

sram_cs_n

: NODE; -- node is low when either sram_cs is active low

WriteNVRAM_n

: NODE; -- latched low write_n

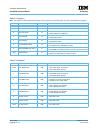

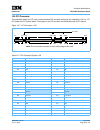

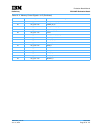

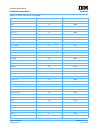

-- | Lboot / LCS0

-- flash_n/sram_sel | bootsmall_n | above boot, boot / upper, lower

-- ============= |==========|=========================================

-- 0 | 0 | SRAM, small flash / big flash

-- 0 | 1 | - big flash - / SRAM, small flash

-- 1 | 0 | small flash, SRAM / big flash

-- 1 | 1 | - big flash - / small flash, SRAM

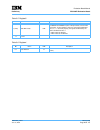

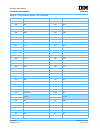

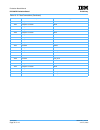

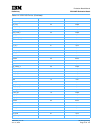

del_nvramcs : lpm_ff WITH (

LPM_WIDTH = 12,enable,aset,

LPM_FFTYPE = "DFF"

);

del_uart : lpm_ff WITH (

LPM_WIDTH = 10,enable,aset,

LPM_FFTYPE = "DFF"

);

halfclk_ : lpm_ff WITH (

LPM_WIDTH = 1,

LPM_FFTYPE = "DFF"

);

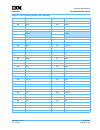

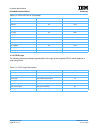

BEGIN

-- basic chip selects

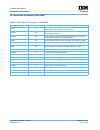

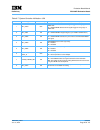

!fpga_cs_n

= !lcs_n[1] & !CSTiming_n; -- lcs1_n chip select

-- divide down 133Mhz clock to make 66MHz clock

halfclk_.enable = !nvram_burst_cs_n;

halfclk_.aset = nvram_burst_cs_n;

halfclk_.clock = sysclk;

halfclk_.data[0] = !halfclk_.q[0];

halfclk = halfclk_.q[0 ];

-- delay nvram_burst_cs_n for nine 66MHz clocks

del_nvramcs.enable = !nvram_burst_cs_n;

del_nvramcs.aset = nvram_burst_cs_n;

del_nvramcs.clock = halfclk;

del_nvramcs.data[0] = gnd;

del_nvramcs.data[1] = del_nvramcs.q[0];

del_nvramcs.data[2] = del_nvramcs.q[1];