IBM PPC750FX User Manual - page 94

Evaluation Board Manual

PPC750FX Evaluation Board

Preliminary

CPLD Programming

Page 94 of 115

750FXebm_ch11.fm

June 10, 2003

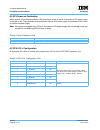

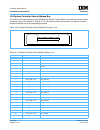

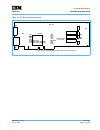

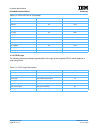

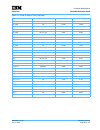

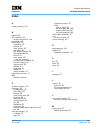

11.2 Timing—Registers and Control Functions

The timing data in the following tables are based on simulation.

11.2.1 Maximum Clock Frequency

provides the actual frequency at which the indicated clock is running, and the highest frequency at

which it can be allowed to run before the period becomes shorter than the worst case signal propagation time.

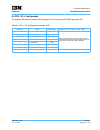

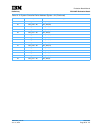

11.2.2 Clock-to-Output Time

provides the longest and shortest input-to-output delay for each output signal clocked through a

register for the all clocks that gate the signal.

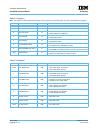

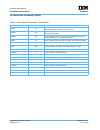

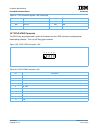

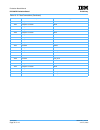

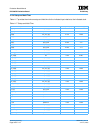

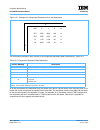

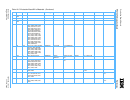

Table 11-4. Maximum Clock Frequency

Clock

Actual Operating Frequency

Allowed Maximum Frequency (period)

pld25mhz

25MHz

166.67 MHz (6ns)

dev_we_n[0]

None

181.82MHz (5.5 ns)

pld_sysclk

133.33MHz

185.19MHz (5.4 ns)

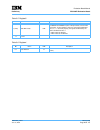

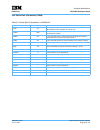

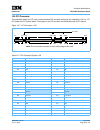

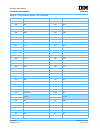

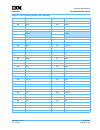

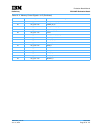

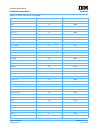

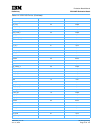

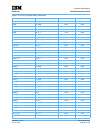

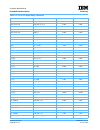

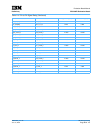

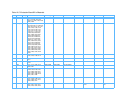

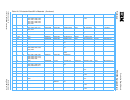

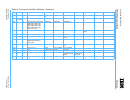

Table 11-5. Clock-to-Output Time

Output Signal

Clock

Longest Delay (ns)

Shortest Delay (ns)

big_flash_cs_n

ale

9.100

9.100

cpu_mcp0

dev_we_n[0]

10.900

10.900

cpu_mcp1

dev_we_n[0]

10.900

10.900

cpu_tben

dev_we_n[0]

10.900

10.900

cpu_trst_n

pld25mhz

26.400

18.500

cpu0_hreset_n

dev_we_n[0]

15.500

15.500

cpu0_hreset_n

pld25mhz

23.100

15.200

cpu0_smi_n

dev_we_n[0]

10.900

10.900

cpu0_sreset_n

dev_we_n[0]

14.700

14.700

cpu0_sreset_n

pld25mhz

14.500

14.400

cpu1_hreset_n

dev_we_n[0]

19.200

19.200

cpu1_hreset_n

pld25mhz

26.800

18.900

cpu1_smi_n

dev_we_n[0]

10.900

10.900

cpu1_sreset_n

dev_we_n[0]

14.700

14.700

cpu1_sreset_n

pld25mhz

14.500

14.400

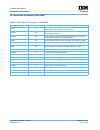

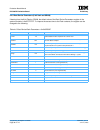

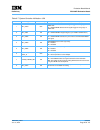

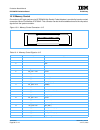

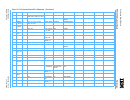

dev_adr[0]

ale

12.500

12.500

dev_adr[0]

dev_we_n[0]

9.500

9.400

dev_adr[1]

ale

12.500

12.500

dev_adr[1]

dev_we_n[0]

9.400

9.400

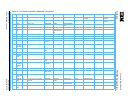

dev_adr[2]

ale

12.500

12.500