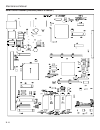

Tally T6090 Maintenace Manual - page 19

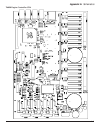

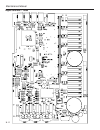

Chapter 1: Electronic Hardware Architecture, Performance & Specifications

1–3

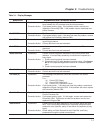

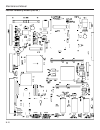

Serial and Parallel Interfaces

Serial

•

MC145406 (+/- 12V) chip is used for the RS-232 drivers and receivers

•

Internal programmable bps generator (300 bps to 38.4K bps)

•

Both DTR/Busy and XON/XOFF is supported

•

Standard secondary RTS on pins 11 and 19. Primary RTS is capable of being

jumpered to pin 4

Parallel

•

Altera EPM7064 and 74LS374/74LS244 – supports IEEE-1284 compatibility and

nibble modes

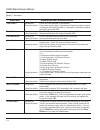

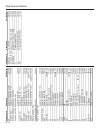

Motorola MC68340

•

25MHz clock

•

16-bit CPU bus

•

Two direct Memory Access (DMA) channels – One for hammer loading, and one for

the IEEE-1284 parallel Interface

•

Two serial channels – One for the control CPU communication, and one for the

external serial interface

Flash Memory

The amount of Flash Memory depends on the configuration of the personality module.

DRAM

The amount of DRAM depends on the configuration of the personality module.

Altera EPM7064

•

Dynamic random access memory (DRAM) control

•

Logic for IEEE-1284 Parallel interface

•

Glue logic (chip selects, hammer data and clock, row and column selection for

DRAM)